Project information

- Category: Senior Capstone Project

- Client: Iowa State University

- Project date: 2020-2021

- Project URL: http://199.66.13.200/index.html

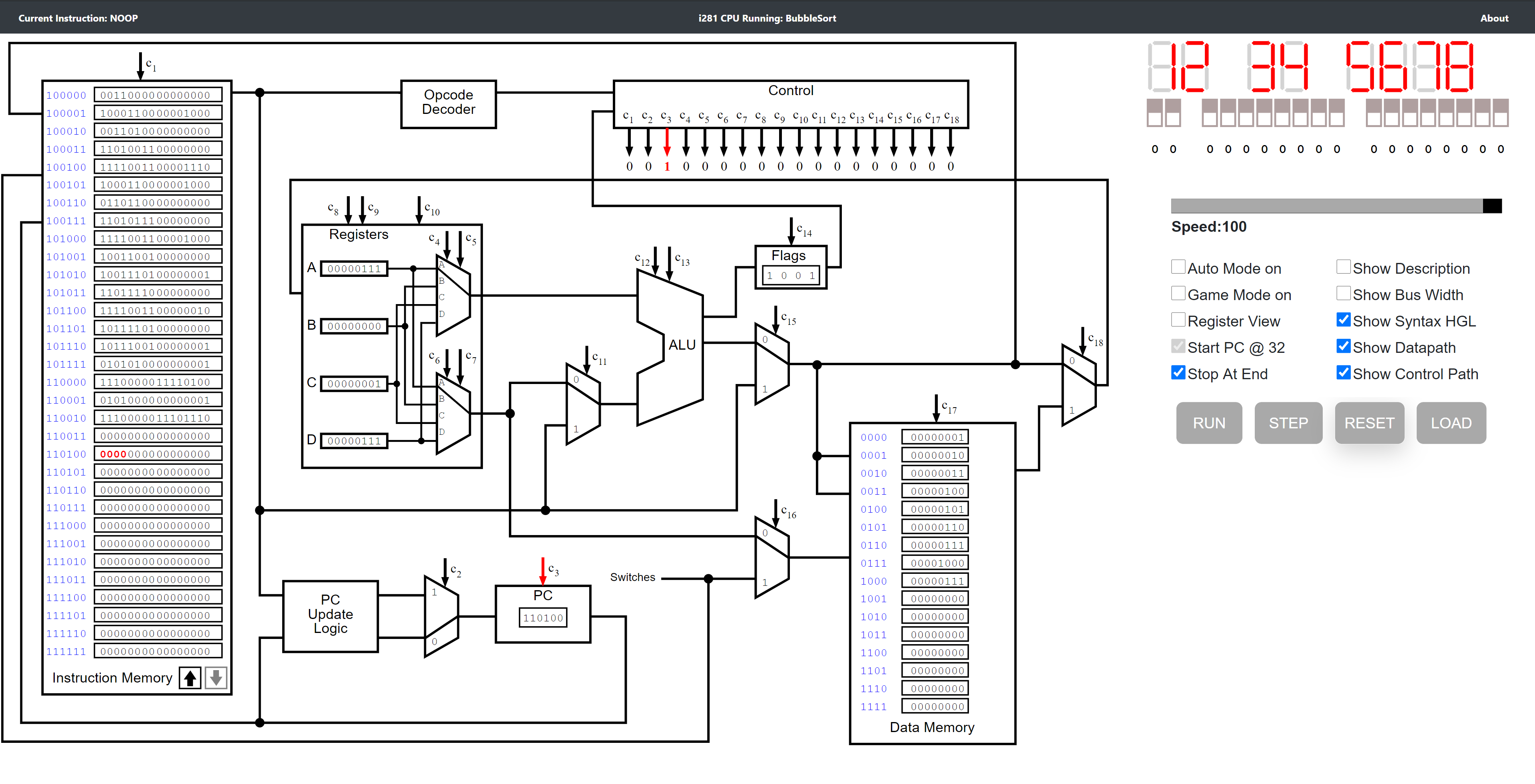

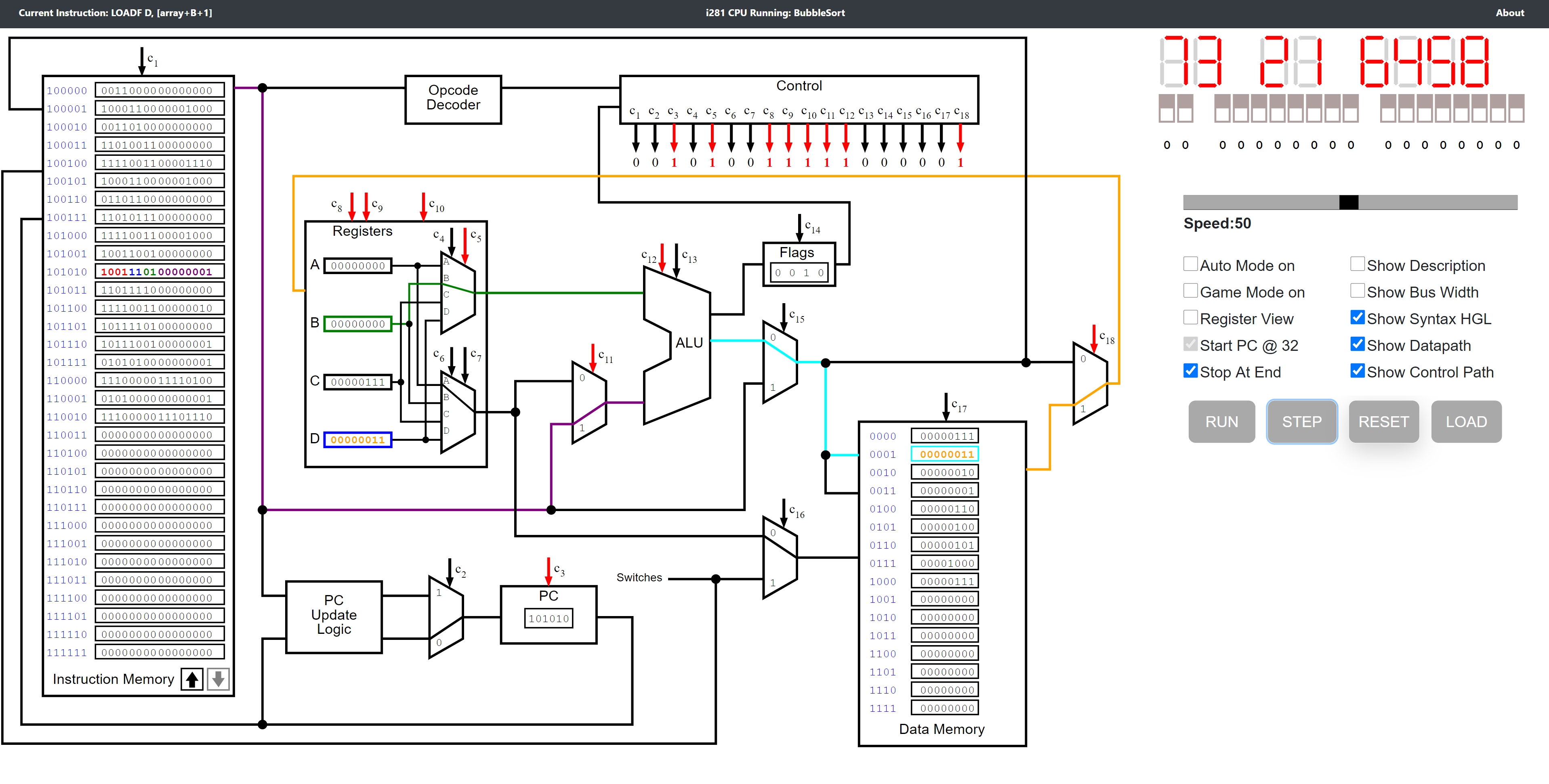

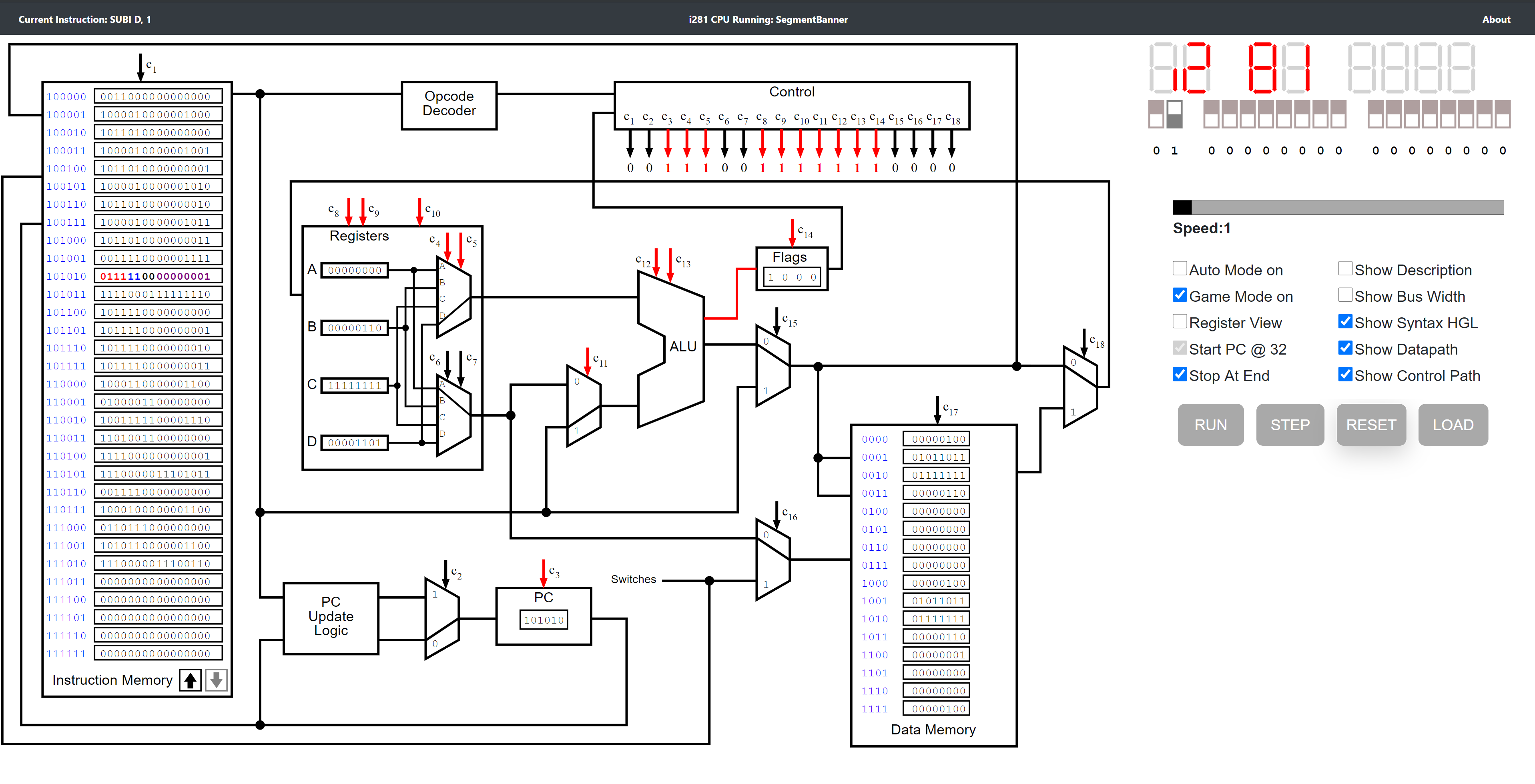

Visual Debugger for the i281 CPU

Project Background

The i281 CPU is a processor conceptualized and designed by Dr. Stoytchev and former TA Kyung-Tae Kim. It was created, verified, and simulated using exclusively the DE2-115 FPGA. It is a 16 bit processor designed completely in Quartus using simple logic to teach students how the culmination of knowledge taught in CprE 281 (Iowa State’s digital logic course) can be used to create a working processor that can run assembly code.

The course builds from boolean algebra into designing complex circuits. Since the course is often a student's first course in the Computer Engineering curriculum, it is challenging to understand at first. At the end of the semester the course introduces assembly code and the fundamentals of a processor, which are very abstract concepts to understand. This is why we are creating a simulation to explain the concept in an in depth and responsive manner. It also works to show students how the connection between assembly and machine code works, as in his original presentations Dr. Stoytchev focuses heavily on how the bits propagate through the processor from the machine code assembled by his custom assembler.

Problem Statement

Due to the requirement of having a DE2-115 FPGA, it would be difficult for students to experience and understand many of the concepts that are taught with this new material, and it is advantageous to do so as another course within the program, CprE 381(Computer Architecture), will require students to learn these ideas in depth to implement their own 32 bit processor that can run standard MIPS assembly language.

As a result of his desire for students to easily access and understand this knowledge, this project was created to help students learn how a CPU works without the strict requirements of the original design.

Problem Solution and Goals

The project is a web app CPU simulation. The user will be able to input assembly language into the JavaScript assembler that we developed, which will in turn translate, or assemble, the inputted assembly into machine code. The assembler will offer a visual component to teach the conversion of assembly to machine code. The visualizer will have access to the values stored within the CPU simulation, and will be able to update certain components to reflect what is happening within the simulation.

In order to mimic the DE-115 FPGA as much as possible, certain aspects of the I/O are also replicated, namely the switches used for input, and the seven-segment displays that are used for outputting values in memory/registers. See Figure 2 below as reference.

Through this project we want to accomplish a working understandable CPU. The main goal is to have the CPU be easy to understand and also simple enough that any user can learn from the app as they work through it.

Aside from this, in order to make future testing and development easier it was also requested that a Verilog version of the project be developed as well, since the original project was exclusively made using block diagram files in Quartus. Along with this, general refactoring and cleaning up of the original BDF files took place to increase readability, and as a result understandability as well.