Project information

- Category: 381 Final Project

- Client: Iowa State University

- Project date: 2019

Mars Rover

Project Description

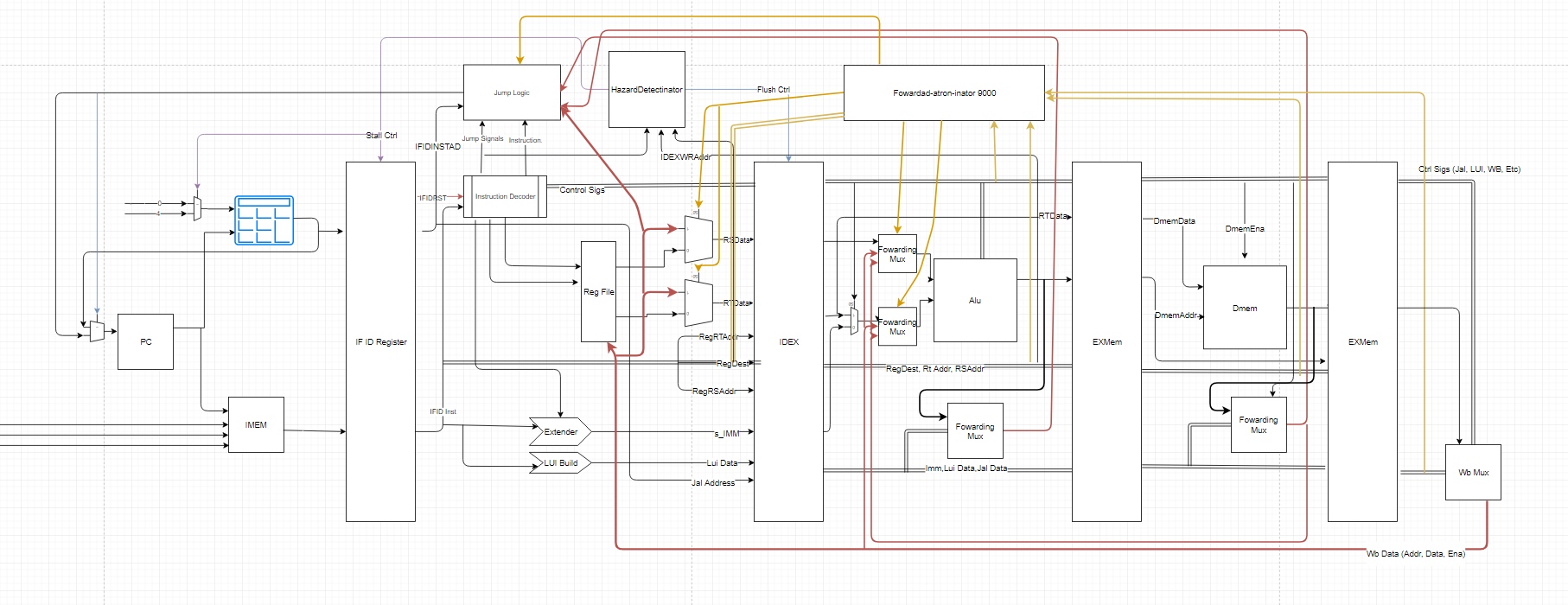

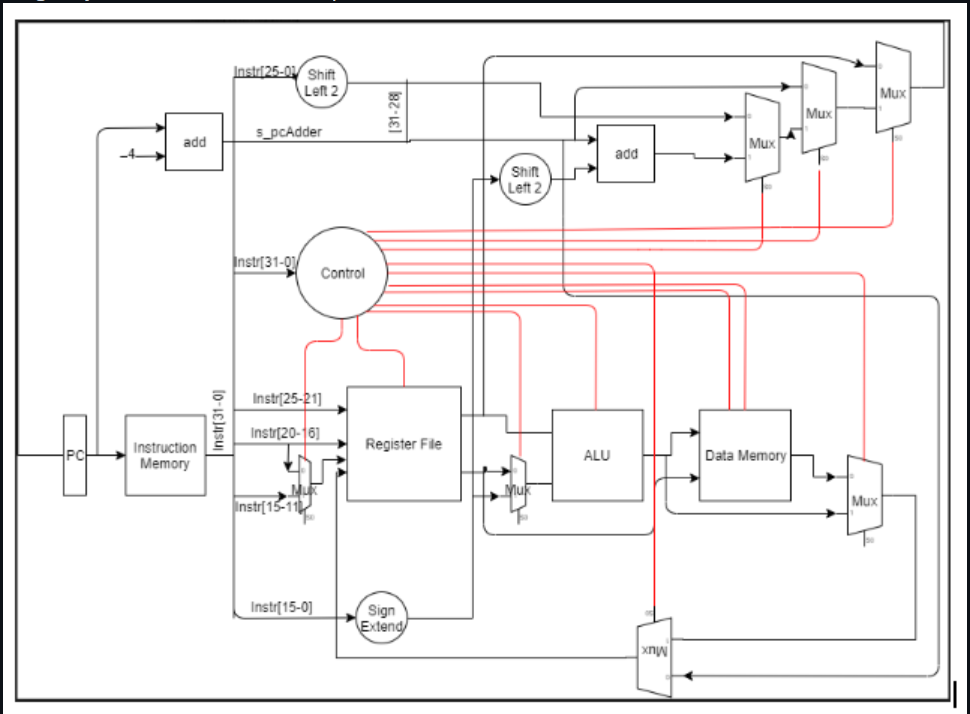

This pipelined processor was built using VHDL and runs MIPS assembly code. We started by making a single cycle CPU (Shown in the slides above), which took one instruction at a time. Register File - This is a 32 by 32-bit32-bit register file. The main product here is the "MipsProccessor". It can process Addi, Add, Sub, and Subi with the 32-bit registers made in the register file.

Memory Interface - This is building onto the last processor and can do the previous instructions and lw and sw